ND-100 Registers

Jump to navigation

Jump to search

ND-100 CPU registers and organisation

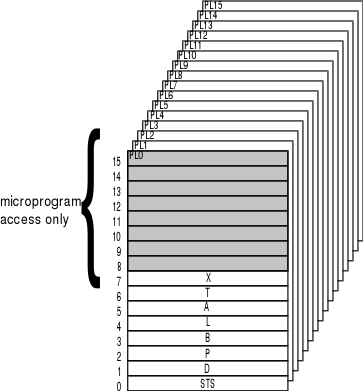

Register File

The ND-100 CPU has a register file of 256 registers, organised as 16 registers on 16 different runlevels. Of those 16 registers, the top 8 are only accessible by the microprogram. On switch between runlevels, the current register set is stored in the register file from the ALU and the new one is loaded.

Internal registers

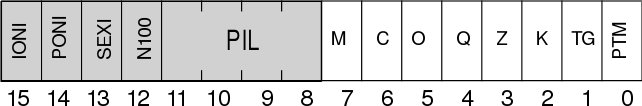

STS

The Status register STS is formed by having a common upper 8 bits and the lower 8 is separate for each program level.

- IONI - Interrupt system ON indicator.

- PONI - Memory management ON indicator.

- SEXI - Extended indicator to show that MMS is in 24 bits extended addressing mode instead of the usual 19 bits addressing mode.

- N100 - N100 indicator to tell the operating system that this is a ND-100 machine.

- PIL - Current program level indicator.

- M - multishift link indicator. Temporary storage for discarded bits in shift instructions, used to ease the shifting of multiple precision words.

- C - Carry indicator.

- O - Static overflow indicator. Remains set after an overflow condition until reset by program.

- Q - Dynamic overflow indicator.

- Z - Error indicator. Static and thus remains set until reset by program. The Z indicator may be internally connected to an interrupt level such that an error message routine may be triggered.

- K - One bit accumulator. Used by the BOP instructions operating on one bit data.

- TG - Rounding indicator for floating point operations.

- PTM - Page table modus. Enables use of the alternate page table.

These indicators are fully program controlled either by means of the BOP instruction or the TRA or TRR instructions where all indicators may be transferred to and from the A register.

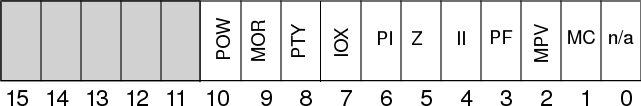

IIE

The Internal Interrupt Enable Register controls the internal interrupt system

- POW - Power fail interrupt.

- MOR - Memory out of range, addressing non-existent memory.

- PTY - Memory parity error.

- IOX - IOX error, no answer from external device.

- PI - Privileged instruction.

- Z - Error indicator, the Z indicator is set.

- II - Illegal instruction.

- PF - page fault, page not in memory.

- PV - Protect violation. Page number is found in the Paging Status Register.

- MC - Monitor call.

- n/a - Not assigned.

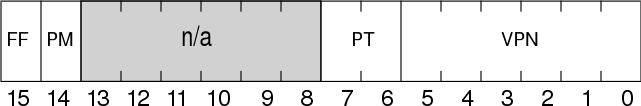

PGS

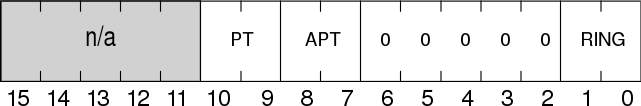

PCR

Sources

- Norsk Data Document ND–06.014 ND-100 REFERENCE MANUAL (ND-06.014.02 rev A)