ND-100: Difference between revisions

(Fixed links to pictures) |

(→Sources: Fixing templates) |

||

| Line 331: | Line 331: | ||

== Sources == | == Sources == | ||

*{{ | *{{OriginWP-EN|NORD-100|4th August 2008}} | ||

* ND- | *{{ND-doc|06.014|(ND-06.014.02 rev A)}} | ||

* ND-100 Instant Instruction Codes (ND-06.021Q02 12/83) | * ND-100 Instant Instruction Codes (ND-06.021Q02 12/83) | ||

Revision as of 21:33, 21 October 2008

The ND-100 was a 16-bit minicomputer series made by Norsk Data, introduced in 1979. It shipped with the SINTRAN III operating system, and the architecture was based on, and backwards compatible with, the NORD-10 line.

The NORD-100 was originally named the NORD-10/M (M for Micro) as a bitsliced OEM processor. The board was laid out and finished and tested when they realized that the CPU was far faster than the NORD-10/S. The result was that all the marketing material for the new NORD-10/M was discarded, the board was rechristened the NORD-100, and extensively advertised as the successor of the NORD-10 line. Later, in an effort to internationalize their line, the machine was renamed ND-100.

Performance

| ND-100 | ND-100/CE | ND-110 | ND-110/CX | ND-120/CX | ND-125/CX | |

|---|---|---|---|---|---|---|

| Minimum number of microinstructions per instruction | 3 | 3 | 1 | 1 | ||

| Minimum microinstruction cycle time | 150ns | 150ns | 100ns | 100ns |

CPU

The ND-100 line used a custom processor, and like the PDP-11 line, the CPU decided the name of the computer.

- NORD-100/CE, Commercial Extended, with decimal arithmetic instructions (The decimal instruction set was later renamed CX)

- ND-110, incrementally improved ND-100

- ND-110/CX, an ND-110 with the decimal instructions.

- ND-120/CX, completely redesigned.

The ND-100 line was machine-instruction compatible with the Nord-10 line, except for some "extended instructions", all in supervisor mode, mostly used by the operating system. Like most processors of its time, the native bit grouping was octal, despite the 16-bit word length.

The ND-100 series had a microcoded central processing unit, with downloadable microcode, and was considered a CISC processor.

ND-100

The ND-100 was implemented using medium-scale integration (MSI) logic and bit-slice processors.

The ND-100 was frequently sold together with a memory management card, the MMS. The combined power use of these boards was 90 watts. These boards would usually occupy slots 2 and 3, for the CPU and MMS, respectively. Slot 1 was reserved for the Tracer, a hardware debugger system.

ND-100/CE

The CE stood for Commercial Extended. The processor was upgraded by replacing the microcode PROM.

It added instruction for decimal arithmetic and conversion, stack instructions, segment-change instructions used by the OS, a block move, test-and-set, and a read-without-cache instruction.

ND-110

The ND-110 was an incremental improvement over the ND-100.

The ND-110 combined the Memory Management System and CPU, previously separate cards, on one board. The single CPU/MMS board was plugged into the memory management board slot, usually numbered 3. The power consumption was reduced from 90 watts to 60.

The ND-110 made extensive use of PALs and gate arrays - with "semi-custom" VLSI chips.

The ND-110 had three gate arrays:

- The Micro Instruction Controller, the MIC - also known as RMIC, for "Rask MIC" ("Speedy MIC"). It replaced three 74S482 sequencers and about 30 other ICs.

- The Arithmetical and Logical Unit gate array (ALU, also known as the "BUFALU"). Replaced four Am2901 bit-slice processors, and some additional registers like the data bus register the general purpose register, and the internal register block.

- The Micro Address Controller (The MAC, also called RMAC, for "Rask MAC" ("Speedy MAC"). It implemented hardware address arithmetic, which in the ND-100 had been done in microcode.

In addition to the macro-instruction cache memory also found in the ND-100, the ND-110 had a unique implementation of cache memory on the micro-instruction level. The step known as mapping in the ND-100 was then avoided because the first micro-instruction word of a macro-instruction was written into the control store cache.

Unlike the ND-100 CPU, it handled synchronous interrupts as traps, similar to how it was handled by the ND-500.

The control store consisted of 4K x 4 bit 40ns SRAM chips. This meant that the control store was writable. It was loaded at power up and Master Clear from two 32Kx8 bit EPROMs.

The CPU clock and the bus arbitration network were implemented using 15ns PALs.

The main oscillator was a 39.3216 MHz crystal oscillator.

ND-110/CX

This was the ND-110 with the CX microcode PROM. The added instructions were the same as the /CE.

ND-120/CX

The ND-120 CPU was a complete reimplementation on an LSI chip (The so-called Delilah chip), and was originally intended to be sold as the ND-1000, to reflect the technology change, which paralleled the change from the ND-500 series to the ND-5000 (Codenamed Samson).

The Samson/Delilah naming scheme may reflect that around the time of the development of the ND-120, it was increasingly clear that the mixed 16/32-bit architecture was a bottleneck for the ND-500(0) architecture; Internal technical documentation used at Norsk Data for the Delilah chip has a drawing of a grinning woman with hair in her clenched fist.

==This is the place where I thought to add information about the Nord 100 minicomputer, and document the instruction set etc.==

ND100 Boot Loaders

The ND100 has bootstrap loaders for mass storage and character oriented devices. There is two load formats.

- Binary load format.

- Mass storage load.

Binary load format

A, B and C (all in grey) are optional.

- A - Any characters not including ! (ASCII 33).

- B - Octal number (any number of digits) terminated with a CR (linefeed is ignored).

- C - Octal number (any number of digits).

- ! - Termination character of header.

- D - Block start address. Presented as two bytes, most significant byte first.

- E - Word count of block F. Presented as two bytes, most significant byte first.

- F - Binary data. Each word presented as two bytes, most significant byte first.

- G - Checksum word. Presented as two bytes, most significant byte first. The checksum is the 16 bit arithmetic sum of all words in F.

- H - Action code. A bit fuzzy in the manual about which of B or C is used.

Binary load is started by typing:

<physical device address>& or <physical device address>$

Loading will take place from the specified device. This device must conform with the programming specifications of either Teletype or tape reader. The device address is the lowest address associated with the device. Binary load will be performed if & or $ is written (or the LOAD button is pressed) and the switch selected ALD has bit 13 equal to "0".

If no device address precedes the & command, then the & is equivalent to pushing the LOAD button on the operator's panel.

If a checksum error is detected, "?" is typed on the console and control is returned to the operator's communication.

Note that the binary loader does not require any of the main memory.

The binary load will change the registers on level 0.

The binary load format is compatible with the format dumped by the )BPUN command in the MAC assembler.

Mass storage load

Mass storage load is started in the same way as binary format load, except that bit 13 in the device address should be a "1".

When loading from mass storage, 1K words will be read from mass storage address 0 into main memory starting in address 0. After a successful load, the CPU is started in main memory address 0.

The mass storage device must conform with either drum or disk programming specifications.

ND100 CPU registers and organisation

Register File

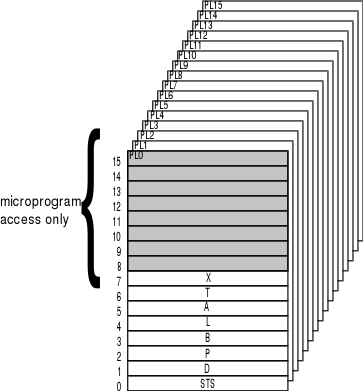

The ND100 CPU has a register file of 256 registers, organised as 16 registers on 16 different runlevels. Of those 16 registers, the top 8 are only accessible by the microprogram. On switch between runlevels, the current register set is stored in the register file from the ALU and the new one is loaded.

Internal registers

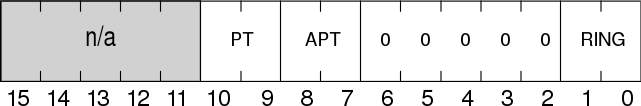

STS

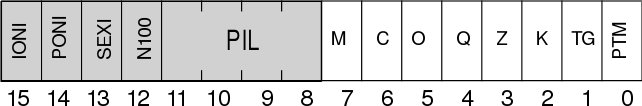

The Status register STS is formed by having a common upper 8 bits and the lower 8 is separate for each program level.

- IONI - Interrupt system ON indicator.

- PONI - Memory management ON indicator.

- SEXI - Extended indicator to show that MMS is in 24 bits extended addressing mode instead of the usual 19 bits addressing mode.

- N100 - N100 indicator to tell the operating system that this is a ND100 machine.

- PIL - Current program level indicator.

- M - multishift link indicator. Temporary storage for discarded bits in shift instructions, used to ease the shifting of multiple precision words.

- C - Carry indicator.

- O - Static overflow indicator. Remains set after an overflow condition until reset by program.

- Q - Dynamic overflow indicator.

- Z - Error indicator. Static and thus remains set until reset by program. The Z indicator may be internally connected to an interrupt level such that an error message routine may be triggered.

- K - One bit accumulator. Used by the BOP instructions operating on one bit data.

- TG - Rounding indicator for floating point operations.

- PTM - Page table modus. Enables use of the alternate page table.

These indicators are fully program controlled either by means of the BOP instruction or the TRA or TRR instructions where all indicators may be transferred to and from the A register.

IIE

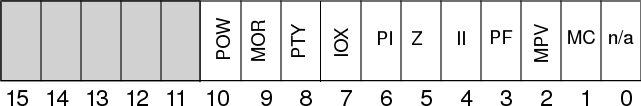

The Internal Interrupt Enable Register controls the internal interrupt system

- POW - Power fail interrupt.

- MOR - Memory out of range, addressing non-existent memory.

- PTY - Memory parity error.

- IOX - IOX error, no answer from external device.

- PI - Privileged instruction.

- Z - Error indicator, the Z indicator is set.

- II - Illegal instruction.

- PF - page fault, page not in memory.

- PV - Protect violation. Page number is found in the Paging Status Register.

- MC - Monitor call.

- n/a - Not assigned.

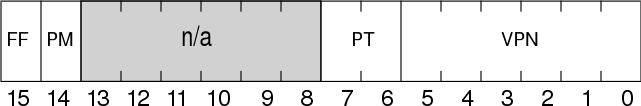

PGS

PCR

Instruction Set

Memory Reference Instructions

Store Instructions

Load Instructions

Arithmetic and Logical Instructions

Double Word Instructions

Floating Instructions

Byte Instructions

Execute Instruction

Bit Instructions

Shift Instructions

System Control Instructions

Transfer Instructions

Load Independent Instructions

Inter-level Instructions

Register Operations

Arithmetic Operations, RAD=1:

C,O,Q may be affected by the following operations

Logical Operations, RAD=0:

Combined Instructions:

Extended Arithmetic Operations:

Floating Conversion

Memory Examine/Deposit Instructions

Sequencing Instructions

Unconditional Jump

Conditional Jump

Skip Instructions

See also

For more information look at Wikipedia:NORD-100

Sources

- This article was originally a copy of the English Wikipedia article NORD-100 in 4th August 2008.

- Norsk Data Document ND–06.014 ND-100 REFERENCE MANUAL (ND-06.014.02 rev A)

- ND-100 Instant Instruction Codes (ND-06.021Q02 12/83)