3202: Difference between revisions

(added ECO section and information about ECO X01) |

m (→Microcode) |

||

| (15 intermediate revisions by 3 users not shown) | |||

| Line 1: | Line 1: | ||

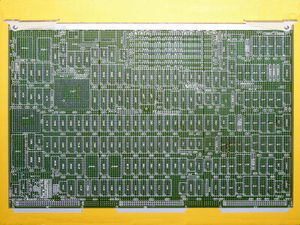

[[Image:ND120-CPU-board-component.jpg | thumb | ND 120 CPU board, component side.]] | [[Image:ND120-CPU-board-component.jpg | thumb | ND 120 CPU board, component side.]] | ||

[[Image:ND120-CPU-board-solder.jpg | thumb | ND 120 CPU board, solder side.]] | [[Image:ND120-CPU-board-solder.jpg | thumb | ND 120 CPU board, solder side.]] | ||

'''3202''' is the [[ND-120]] CPU board. | '''3202''' is the [[ND-120/CX]] CPU board. The same identifier (variants 350175/350176/350177/350178) is used for [[ND-125/CX]] CPU boards. The difference is that the 125/CX has faster on-board memory access and includes more on-board memory (8/12/16 MB, the 120/CX can have up to 6MB RAM on-board).<ref>http://sintran.com/sintran/hardware/hw-nd-100.html</ref> | ||

{{Stub}} | {{Stub}} | ||

==Introduction== | |||

It contains the CPU, bus arbitration logic, memory control, memory and other subsystems. It also has the Real time clock and the I/O for the serial console. | |||

==Switches and indicators== | |||

* SW3 - Master Clear - normal position = central. This switch may be depressed to give a hardware master clear to the CPU. | |||

* TH1 - ALD select | |||

* TH2 - Baud rate select | |||

* LED3 - self test passed (green) | |||

* LED2 - self test fail (red) | |||

* LED1 - cache OFF (red) | |||

* SW1 - Cache ON, normal position = down. | |||

* LED6 - CPU grant (green) | |||

* LED7 - bus grant (yellow) | |||

* SW2 - Memory OFF, normal position = down. | |||

* LED4 - parity error (red) | |||

* LED5 - parity disable (red) | |||

* SW4 - Parity disable, normal position = down. | |||

* upper limit display | |||

** 000 - memory off (SW2) | |||

** 100 - 2M Bytes onboard memory | |||

** 200 - 4M Bytes onboard memory | |||

** 300 - 6M Bytes onboard memory | |||

==Connectors== | |||

The A and B connectors are used for I/O, the C connector is used for the [[ND-100 Bus]]. | |||

==I/O Devices on the card== | |||

none? | |||

== ECO == | == ECO == | ||

ECO or Engineering Change Order is a hardware change. Here is a list of known ECO's for this card. | ECO or Engineering Change Order is a hardware change. Here is a list of known ECO's for this card. | ||

* ECO | * ECO 100-751 - Gives false interrupt, IOX error, MOR or Protect violation<ref name="ECO"></ref> | ||

* ECO 100-752 - Sintran corruption when heavy load on the bus<ref name="ECO"></ref> | |||

* ECO 100-763 - Sintran hangs or gives ILLEGAL INSTRUCTION.<ref name="ECO"></ref> | |||

* ECO 100-774 - Memory out of range<ref name="ECO">sintran.com, Norsk Data library, ECO [http://sintran.com/sintran/library/libeco/libeco.html]</ref> | |||

* ECO 100-779 - System failing with cache enabled<ref name="ECO"></ref> | |||

* ECO 100-785 - Memory out of range, IOX-error<ref name="ECO"></ref> | |||

* ECO 100-786 - Upgrade ND-120CX CPU & MM 32B 2MB to ND-125CX<ref name="ECO"></ref> | |||

* ECO X01 - New backup battery for the calendar on ND-120 CPU<ref name="ECO"></ref> | |||

==Part numbers== | |||

(Printed on the edge of the PCB) | |||

{| class="wikitable" | |||

|- | |||

! PART NO. !! NAME !! PRINT | |||

|- | |||

| 350002 || ND-120/CX 32-BIT 6 MB || 3202 | |||

|- | |||

| 350102 || ND-120/CX 48-BIT 6 MB || 3202 | |||

|- | |||

| 350103 || ND-120/CX 32-BIT 4 MB || 3202 | |||

|- | |||

| 350104 || ND-120/CX 48-BIT 4 MB || 3202 | |||

|- | |||

| 350105 || ND-120/CX 32-BIT 2 MB || 3202 | |||

|- | |||

| 350106 || ND-120/CX 48-BIT 2 MB || 3202 | |||

|- | |||

| 350107 || ND-120/CX GEN.VERS. || 3202 | |||

|- | |||

| 350108 || ND-120 32-BIT 6 MB || 3202 | |||

|- | |||

| 350109 || ND-120 48-BIT 6 MB || 3202 | |||

|- | |||

| 350110 || ND-120 32-BIT 4 MB || 3202 | |||

|- | |||

| 350111 || ND-120 48-BIT 4 MB || 3202 | |||

|- | |||

| 350112 || ND-120 32-BIT 2 MB || 3202 | |||

|- | |||

| 350113 || ND-120 48-BIT 2 MB || 3202 | |||

|} | |||

== Microcode == | |||

The microcode for the CPU is held in two EPROMs, type AM 27256 32KB.[[File:3202_microcode_Roms.png|200px|thumb|right|3202 - EPROMs with microcode]] | |||

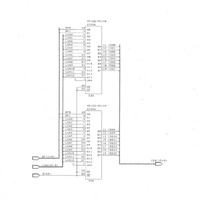

[[File:3202_CPU_EPROM.png|200px|thumb|right|3202 - Schematic for microcode EPROMs ]] | |||

The location for these EPROMS is 23B and 26B | |||

Location: the board has letters for rows (A, B, C, ...) on the left edge, and numbers (1, 2, 3, ...) at the top edge. | |||

Location of any given component on the board is given as a number and single letter (for small components) or as a series of letters and numbers (for larger components, covering more than one row and / or column). | |||

Dumps of the chips, made with a EPROM programmer. 32 bits floating point format. | |||

* Top chip: [[File:AM27256_45132L_B22.bin.bz2]] Location on board: 23B (bits 0-7) | |||

* Bottom chip: [[File:AM27256_45133L_B24.bin.bz2]] Location on board: 26B (bits 8-15) | |||

This is version L (100014/oct) of the microcode. | |||

(which appears to be a minor bugfix from K version, in the ELEAV function) | |||

Version L seems to be the last version available for the 3202 board. | |||

The PROM's come in two different versions | |||

* 32 Bit floating point format | |||

* 48 Bit floating point format | |||

{| class="wikitable" | |||

|+ PROM options for the 3202D board | |||

|- | |||

!Pos. no. !! Device !! Max. delay !! Stock no. !! Reg. no. !! Floating format !! Bit no. | |||

|- | |||

| 23B || 27256 || 250ns || 500854 || 45132L || 32 bit || 0-7 | |||

|- | |||

| 26B || 27256 || 250ns || 500854 || 45133L || 32 bit || 8-15 | |||

|- | |||

| 23B || 27256 || 250ns || 500854 || 45148L || 48 bit || 0-7 | |||

|- | |||

| 26B || 27256 || 250ns || 500854 || 45149L || 48 bit || 8-15 | |||

|} | |||

== Reference == | == Reference == | ||

<references/> | <references/> | ||

*{{ND-doc|30.008.3 EN}}, page 255 | |||

[[Category:ND-100 hardware]] | [[Category:ND-100 hardware]] | ||

Latest revision as of 15:33, 17 June 2023

3202 is the ND-120/CX CPU board. The same identifier (variants 350175/350176/350177/350178) is used for ND-125/CX CPU boards. The difference is that the 125/CX has faster on-board memory access and includes more on-board memory (8/12/16 MB, the 120/CX can have up to 6MB RAM on-board).[1]

|

|

This article is a stub. You can improve NDWiki by expanding it. |

Introduction

It contains the CPU, bus arbitration logic, memory control, memory and other subsystems. It also has the Real time clock and the I/O for the serial console.

Switches and indicators

- SW3 - Master Clear - normal position = central. This switch may be depressed to give a hardware master clear to the CPU.

- TH1 - ALD select

- TH2 - Baud rate select

- LED3 - self test passed (green)

- LED2 - self test fail (red)

- LED1 - cache OFF (red)

- SW1 - Cache ON, normal position = down.

- LED6 - CPU grant (green)

- LED7 - bus grant (yellow)

- SW2 - Memory OFF, normal position = down.

- LED4 - parity error (red)

- LED5 - parity disable (red)

- SW4 - Parity disable, normal position = down.

- upper limit display

- 000 - memory off (SW2)

- 100 - 2M Bytes onboard memory

- 200 - 4M Bytes onboard memory

- 300 - 6M Bytes onboard memory

Connectors

The A and B connectors are used for I/O, the C connector is used for the ND-100 Bus.

I/O Devices on the card

none?

ECO

ECO or Engineering Change Order is a hardware change. Here is a list of known ECO's for this card.

- ECO 100-751 - Gives false interrupt, IOX error, MOR or Protect violation[2]

- ECO 100-752 - Sintran corruption when heavy load on the bus[2]

- ECO 100-763 - Sintran hangs or gives ILLEGAL INSTRUCTION.[2]

- ECO 100-774 - Memory out of range[2]

- ECO 100-779 - System failing with cache enabled[2]

- ECO 100-785 - Memory out of range, IOX-error[2]

- ECO 100-786 - Upgrade ND-120CX CPU & MM 32B 2MB to ND-125CX[2]

- ECO X01 - New backup battery for the calendar on ND-120 CPU[2]

Part numbers

(Printed on the edge of the PCB)

| PART NO. | NAME | |

|---|---|---|

| 350002 | ND-120/CX 32-BIT 6 MB | 3202 |

| 350102 | ND-120/CX 48-BIT 6 MB | 3202 |

| 350103 | ND-120/CX 32-BIT 4 MB | 3202 |

| 350104 | ND-120/CX 48-BIT 4 MB | 3202 |

| 350105 | ND-120/CX 32-BIT 2 MB | 3202 |

| 350106 | ND-120/CX 48-BIT 2 MB | 3202 |

| 350107 | ND-120/CX GEN.VERS. | 3202 |

| 350108 | ND-120 32-BIT 6 MB | 3202 |

| 350109 | ND-120 48-BIT 6 MB | 3202 |

| 350110 | ND-120 32-BIT 4 MB | 3202 |

| 350111 | ND-120 48-BIT 4 MB | 3202 |

| 350112 | ND-120 32-BIT 2 MB | 3202 |

| 350113 | ND-120 48-BIT 2 MB | 3202 |

Microcode

The microcode for the CPU is held in two EPROMs, type AM 27256 32KB.

The location for these EPROMS is 23B and 26B

Location: the board has letters for rows (A, B, C, ...) on the left edge, and numbers (1, 2, 3, ...) at the top edge. Location of any given component on the board is given as a number and single letter (for small components) or as a series of letters and numbers (for larger components, covering more than one row and / or column).

Dumps of the chips, made with a EPROM programmer. 32 bits floating point format.

- Top chip: File:AM27256 45132L B22.bin.bz2 Location on board: 23B (bits 0-7)

- Bottom chip: File:AM27256 45133L B24.bin.bz2 Location on board: 26B (bits 8-15)

This is version L (100014/oct) of the microcode.

(which appears to be a minor bugfix from K version, in the ELEAV function)

Version L seems to be the last version available for the 3202 board.

The PROM's come in two different versions

- 32 Bit floating point format

- 48 Bit floating point format

| Pos. no. | Device | Max. delay | Stock no. | Reg. no. | Floating format | Bit no. |

|---|---|---|---|---|---|---|

| 23B | 27256 | 250ns | 500854 | 45132L | 32 bit | 0-7 |

| 26B | 27256 | 250ns | 500854 | 45133L | 32 bit | 8-15 |

| 23B | 27256 | 250ns | 500854 | 45148L | 48 bit | 0-7 |

| 26B | 27256 | 250ns | 500854 | 45149L | 48 bit | 8-15 |

Reference

- Norsk Data Document ND–30.008.3 EN ND-100 Hardware Maintenance , page 255